On-Demand Training

Learn at your own pace, how to create 3D views of an Xpedition Layout design, place components, set 3D constraints, and view DRC violations.

A collection of courses and general topics on designing and verifying electronics and electrical circuits and systems and applying EDA tools to automate these tasks. To access this library for free, enter promotional code ExploreVEP__30 in the shopping cart to register.

This course is an introduction to Analog FastSPICE (AFS) Platform. It covers the basics of spice simulation, and AFS features.

The contents of this library will help you learn about the Eldo Platform's rich feature set for accurate, fast interactive analog IC design and verification.

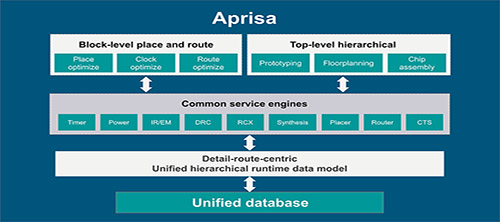

This Library contains various learning paths for entry-level & senior engineers who are interested in expanding their knowledge in Aprisa implementation tool.

Test your skills and knowledge, improve productivity and advance your career. Pass any exam and receive a verifiable badge and certificate. To access this library for free, enter promotional code CERTNOW in the shopping cart.

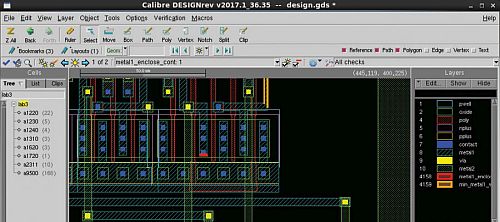

The Calibre library contains a collection of learning paths that will help you master using the tools and the development of application-specific code.

This course is designed for design and foundry engineers to deploy Calibre Multi-Patterning to meet the design to manufacturing needs for technology below 20nm.

Learn how to use both the Pattern Library Manager GUI and SVRF code for pattern capture and pattern comparison.

This learning path will equip you with a basic understanding of Calibre nmOPC, OPCBIAS, nmSRAF, OPCVerify, and modeling basics; there are NO LABS.

This learning path will acquaint you with the many layout manipulation features available in Calibre DESIGNrev.

Learn how to set up and execute Calibre PERC jobs and how to interpret analysis results by working through step-by-step case studies.

Learn how to write DRC and LVS rule checks.

Learn how to write Calibre PERC code for a variety of applications such as ESD protection assessment, electrical over-stress analysis, and chip current density.

Learn how to use Calibre xACT and Calibre xACT 3D to extract parasitics from your IC layout.

The Calibre xRC Parasitic Extraction course will help you learn how to use the powerful Calibre xRC tool to extract parasitic information from your IC layouts

The Catapult High-Level Synthesis (HLS) library contains a set of modules to introduce Engineers to HLS and High-Level Verification. To access this library for free, click buy and enter promotional code ExploreVEP__30 in the shopping cart.

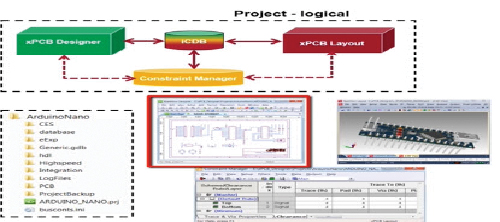

Learn at your own pace using this course. Discover how to use Constraint Manager efficiently and effectively to define and refine design constraints for PCB.

Learn at your own pace using this course. Discover how to use Constraint Manager efficiently and effectively to define and refine design constraints for PCB.

You will gain knowledge of advanced operations of L-Edit IC like SDL and Node Highlighting. You will learn how to use Calibre One for Physical Verification.

This training helps you gain knowledge of basic operations of L-Edit IC to perform physical designs of integrated circuits.

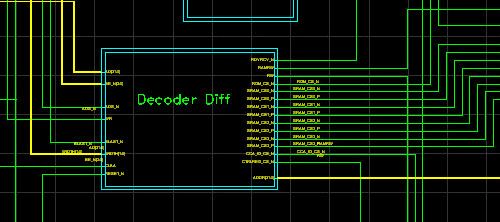

Learn Custom IC Design tools: S-Edit for design capture, simulation, and analysis; L-Edit for IC and MEMs layouts and how it is integrated with Calibre tool.

Learn how to integrate the S-Edit tool with AFS simulator to predict & verify the behavior & performance of the circuit using different types of analysis.

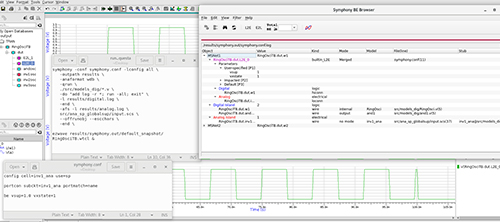

Learn how to integrate the S-Edit tool with the Symphony mixed-signal simulator to simulate analog and digital designs, exploiting AFS simulator's accuracy.

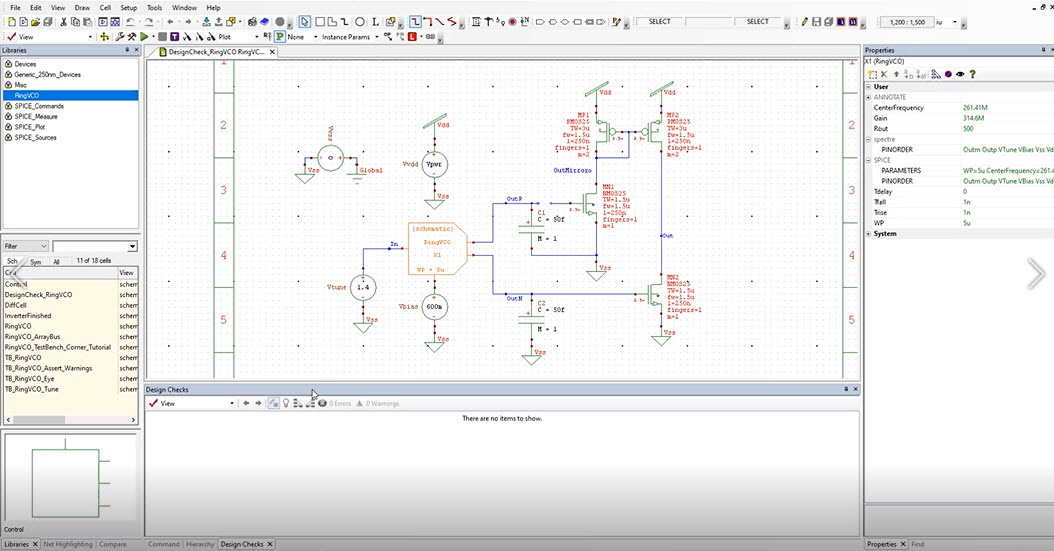

Learn how to leverage the power and sophistication of the Custom IC Design Schematic Entry tool S-Edit for Project Structure and the creation of Schematics.

Learn at your own pace using this course, EDM Library process, load libraries, use sandboxes, create parts and add components and generate cache.

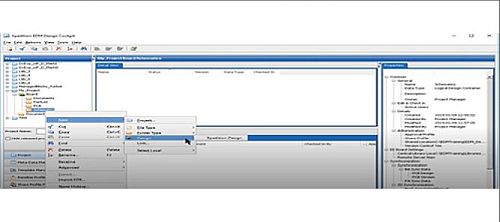

Learn at your own pace using this course, how to use EDM Design Cockpit, and web-based Collaboration capabilities from a designer's perspective.

This library covers how to use EDM Design Cockpit and web-based Collaboration capabilities from a designer’s perspective as well as how to configure the system.

Gain proficiency in installing, configuring and managing a single or multiple EDM Server installations.

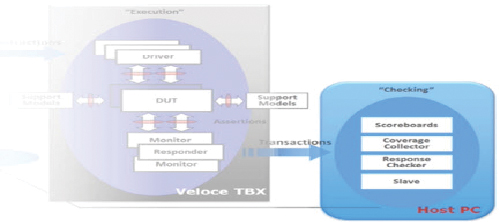

Learn modeling, compilation and runtime debug aspects of emulation with Veloce. This training is applicable to both Veloce2 and Veloce Strato platforms.

Explore Siemens Analog Mixed-Signal Verification Solutions – consistently delivering proven and differentiated capabilities to 1000+ customers worldwide. To access this library for free, click buy and enter promotional code ExploreVEP__30 in the shopping cart.

Explore Siemens Place and route technology for top-level and block-level implementation of complex SoC designs. Find out how the detail-route-centric architecture and hierarchical database can enable you to achieve fast design closure with optimal quality of results. To access this library for free, click buy and enter promotional code ExploreVEP__30 in the shopping cart.

Discover the industry-leading Calibre tool suite capabilities and how this content can solve your day-to-day common IC design problems, including circuit reliability problems, analog layout issues, and other common design challenges. To access this library for free, click buy and enter promotional code ExploreVEP__30 in the shopping cart.

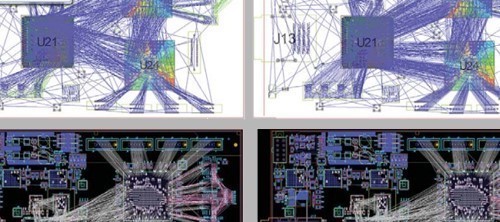

A complete family of analysis tools for high-speed electronic design including DDR, DRC, DC, Signal, Power Integrity, 3D and more. To access this library for free, enter promotional code ExploreVEP__30 in the shopping cart to register.

Discover Questa prime’s advanced verification capabilities. To access this library for free, enter promotional code ExploreVEP__30 in the shopping cart to register.

Explore Siemens custom analog IC design flow to increase productivity from design capture, simulation, physical layout, and verification to tape-out. To access this library for free, enter promotional code ExploreVEP__30 in the shopping cart to register.

Learn at your own pace using this course, how to use the FabLink Drawing Editor tool to prepare multi-page fabrication drawings for a design.

Learn at your own pace using this course, how to use special features of FabLink in both the Panel Editor and Xpedition Layout.

Learn at your own pace using this course, how to use FPGA I/O Optimizer to optimize Multi-FPGA Designs, manage data between PCB and FPGA flows.

You will learn the basics of functional safety and how to run the Siemens tools to measure safety metrics for your designs.

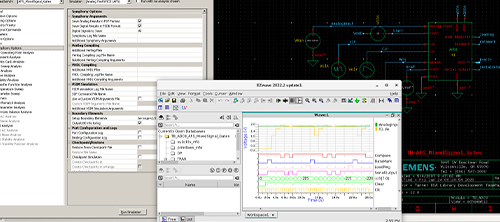

This library contains learning paths that help you master functional verification tools, and the development of test environments using HDL-based methodologies. Learn how to use ModelSim/Questa GUI and command line to verify and debug HDL designs in interactive mode or build batch mode scripts for fast simulations.

Learn core operations of HDL Design Series, how to administer it for team operations and how to implement your company design guidelines for RTL coding.

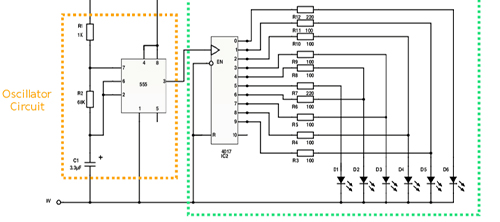

The High Speed Signal Integrity Principles course will help you properly manage the effects of high-speed signals on today’s PCB designs.

A collection of learning paths that cover High Speed PCB design and analysis methodology using HyperLynx family of tools in the new 2409 software release.

Learn how to use HyperLynx SI/PI and Advanced Solvers to perform advanced decoupling analysis, PDN optimization, power-aware analysis, and thermal analysis.

Learn how to use HyperLynx Advanced Solvers to model 3D structures in PCB designs for use in detailed signal and power integrity analysis.

You will learn the basics necessary to analyze a DDR5 interface.

Learn how to effectively use the HyperLynx DDRx Wizard for pre- and post-layout analysis of dual data rate memory interfaces.

Learn how to use HyperLynx DRC to analyze PCB designs to detect and correct EMI, SI, and power problems in designs.

Using the new next generation UX, learn how to use HyperLynx DRC to analyze PCB designs to detect and correct EMI, SI, and power problems in designs.

In this library, you will learn how to use HyperLynx DRC to create a custom rule.

A collection of learning paths that cover High Speed PCB design and analysis methodology using HyperLynx family of tools.

A collection of learning paths that cover High-Speed PCB design and analysis methodology using HyperLynx family of products.

Learn how to use HyperLynx Power Integrity to detect problems and make corrections related to power planes and the thermal behavior of PCB designs.

Using the new 2409 software, learn to use HyperLynx PI to develop constraints, detect & correct DC& AC problems for the power delivery network in your design.

In this course, you will learn how to use the HyperLynx SerDes wizards with 2D and 3D modeling to design optimized serial channels.

In this course you will learn how to use HyperLynx to develop design constraints and to detect and correct signal integrity issues in your designs.

Using the new 2409 software, learn how to use HyperLynx to develop design constraints and detect and correct signal integrity issues in your designs.

Learn at your own pace using this course, how to use Xpedition Package Designer to layout a package, define constraints, route, verify and create docs.

Learn about Innexis™ Virtual System Interconnect multi-domain/multi-fidelity Digital Twin building flow.

The Insight Analyzer course will help you understand how to use the Insight Analyzer tool in your workflow. This tool focuses on leakage and floating gates.

The Level-2 Certification Proctored Exam validates your advanced knowledge of Schematic Entry using Xpedition. Upon registration, you will receive an email to set up your proctor session date and access the exam.

The Level-2 Certification Proctored Exam validates your advanced knowledge of UVM Comprehensive. Upon registration, you will receive an email to set up your proctor session date and access the exam.

Learn at your own pace using this course, how to create, protect, add & change different data types in Central Library using Xpedition Library Manager.

You will learn how to create, protect, add to, and change the different data types in your Central Library using Xpedition Library Manager.

Gain mastery of Advanced Questa Simulator’s capabilities to manage your advanced verification environments and debug verification bugs

Learn how to utilize the power of L-Edit to create, verify and stream in/out MEMS layout efficiently in the shortest time possible.

Learn all about the AMS simulation environment, including how to create and run typical and advanced simulations, analyze results and perform measurements.

Learn the fundamentals of EM and IR drop analysis using the Siemens mPower Power Integrity product line. mPower Analog covers transistor-level analysis, while mPower Digital covers gate-level analysis. These tools provide a complete, scalable solution for IC Power integrity analysis.

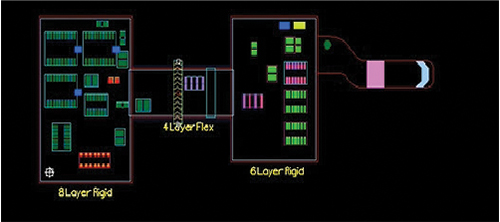

Learn basic concepts, architecture, and workflow of multi-board systems design using Xpedition Systems Designer and Systems Cables.

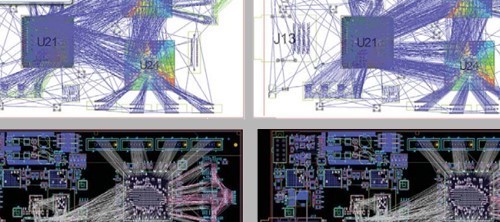

This library covers advanced methods to constraint & route high-speed signals, reducing the time it takes to constraint and route high-speed circuits.

Using the new 2409 software, learn advanced methods to constraint & route high-speed signals, reducing the time it takes to constraint route high-speed circuits.

PADS Professional training library will offer a complete portfolio of learning paths for schematic design, constraint definition, PCB layout, and library creation and management. Free On-Demand Training for PADS Customers. Enter discount code: PADSODT for free access to these PADS training libraries.

This learning path supports designers using the PADS Standard Layout tool in a Netlist flow. It focuses on all areas of PCB design using PADS Layout. Free On-Demand Training for PADS Customers. Enter discount code: PADSODT for free access to these PADS training libraries.

This library will show you how to use PADS Standard Plus to design PCB boards. It contains learning paths for schematic and PCB design. Free On-Demand Training for PADS Customers. Enter discount code: PADSODT for free access to these PADS training libraries.

Learn at your own pace using this course, advanced placement and routing concepts, routing topologies, netline manipulation, MicroVias, delay formulas.

You will learn advanced placement and routing concepts, different routing topologies and netline manipulation, define MicroVias, delay formulas, and much more.

Learn at your own pace using this course, how to integrate a schematic, draw board outline, place components, set constraints, route, and output fab data.

You will learn to integrate a source schematic, draw a board outline, place components, set constraints, route the board, and output the fabrication data.

Learn how to use PowerPro for power analysis/estimation at both RTL and gate-level and how to optimize power during RTL development for the lowest possible design power. To access this library for free, enter promotional code ExploreVEP__30 in the shopping cart to register.

In this methodology-based Library you will learn how to use HyperLynx to identify, analyze and solve design problems for optimum results.

Extend your knowledge of Advanced Questa Simulator features and efficiently analyze and debug HDL code.

Learn to use Advanced Questa Simulator GUI and command line to verify and debug HDL designs in interactive mode or build batch mode scripts for fast simulations.

You will learn how to set up your design in Questa Formal software and how to use AutoCheck, XCheck, CoverCheck and PropCheck to debug and verify your design.

Learn how to use Questa® Lint to perform a fast check of your HDL RTL, looking for completeness and consistency issues.

Learn about the UPF basics, successive refinement flow, & how to use Visualizer Debug Environment with Questa to perform PA verification and debug the results.

In this self-paced course, you will receive an overview of SystemC and learn how to simulate SystemC designs in Questa.

Learn how to create stimulus and check results for standard protocols with Questa Verification IP. Build a UVM testbench or add QVIP to an existing one.

Learn how to use ReqTracer to automate tracing of design requirements to design and test data associated with an FPGA/ASIC design by watching live recordings.

Learn at your own pace using this course, to efficiently implement RF and mixed technology RF designs on an Xpedition PCB Design.

Learn at your own pace using this course, how to use Xpedition Designer to create schematic, select parts using DataBook and prepare for layout.

Gain proficiency in project management, schematic capture, part selection using xDX DataBook, and prepare schematic for layout using Xpedition Designer.

Gain proficiency in project management, schematic capture, part selection using DataBook, and prepare schematic for layout using Xpedition Designer.

Gain proficiency in project management, schematic capture, part selection using DataBook, and prepare schematic for layout using Xpedition Designer within EDM.

This library will help you gain the knowledge needed to harness the power of the S-Edit, AFS, & Symphony to design and verify your analog/mixed ICs

This library will help you gain the knowledge needed to harness the power of the S-Edit, T-SPICE & Waveform Viewer tools to design and verify your analog ICs.

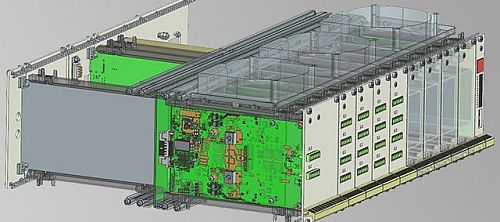

This library contains courses that enable students and educators to become proficient in the Solid Edge portfolio of products. To access this library for free, select the buy option below and enter promotional code SESCUSER in the registration cart to access the learning material.

On demand training for Solid Edge covering various portfolio products including mechanical design, technical publication, CAM and simulation. To access this library for free, enter promotional code SESCUSER in the Registration cart to register.

This is an introduction to the Solido Design Environment. This training course covers its capabilities, including design analysis, optimization, and debugging.

Learn at your own pace using this course, methodology to plan and optimize I/O and connectivity from a chip(s), through multiple packaging scenarios.

This library will help to leverage fast and versatile Symphony tool and its rich feature set to perform accurate mixed-signal simulations.

Learn how to use the Symphony Pro tool and its robust and advanced verification capabilities for mixed-signal designs.

Learn about SystemVerilog fundamental and advanced verification constructs.

Learn about SystemVerilog fundamental and advanced verification constructs through watching video recordings of class presentations, labs and knowledge checks.

This Library focuses on Tcl/Tk and prepares you for mastering “Scripting with DESIGNrev”, “Calibre TVF”, “Rule Writing for Calibre DRC/LVS” and “Coding for PERC

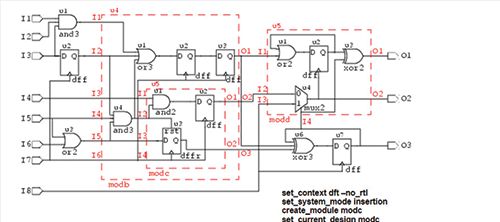

This library of Tessent training courses will enable you to learn about the options for implementing high test quality in your designs.

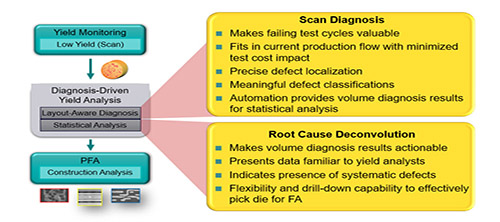

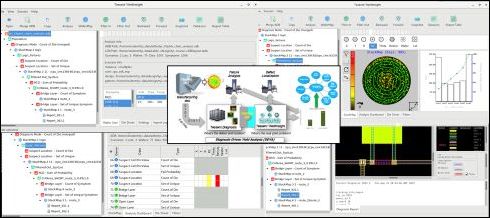

This learning path focuses on Tessent Diagnosis within the Diagnosis Driven Yield Analysis (DDYA) flow.

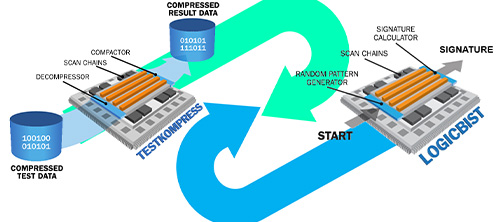

You will learn how to use Tessent TestKompress and LogicBIST together to add both types of logic to your IC to get the benefits of both solutions.

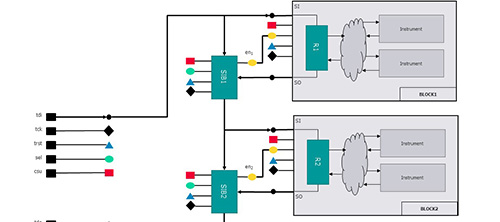

The Tessent IJTAG course covers the details of the IEEE 1687 standard, and how it is used in the Tessent toolset to enable access to the various test IPs.

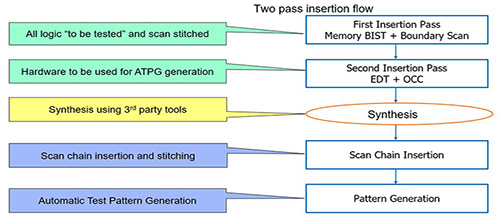

Learn how to implement MBIST, Boundary Scan, IJTAG, Scan Insertion, and TestKompress into your design to obtain high test quality using multiple Tessent tools.

You will learn how to implement DFT for memory test through Tessent Shell tool environment & how to utilize it to implement MemoryBIST solutions for your design.

In this learning path, you will learn about the structure, main concepts, and implementation of Multi-Die devices, as well as their testing and diagnosis.

This learning path will introduce you to scan and ATPG processes. You will gain knowledge on fault models, test pattern types and at-speed testing.

You will learn how to use your Tcl knowledge to perform database introspection for reporting and for design editing for testability improvements.

You will learn how to use Tessent SiliconInsight, and understand the MBIST offline diagnosis flow, as well as ATPG offline diagnosis flow in non-TSDB.

Learn how to leverage the Tessent Shell environment to insert SSN and other test logic into SoCs, generating & verifying test patterns for manufacturing tests.

You will be introduced to Embedded Deterministic Test (EDT) technology, and you will learn how to create compressed test patterns and how to debug EDT DRCs.

This course covers the DDYA process, including is an overview of Tessent Diagnosis and how to use Tessent YieldInsight to identify the true yield limiters.

The University: The CAD Embedded CFD Library offers self-paced learning paths intended for college-level students and faculty. There are NO labs in this library

Introduction to STAR-CCM+ multiphysics simulation, geometry processing, meshing, solver settings, post processing. University edition - there are NO labs. To register for this library for free, use discount code STARUNIV in the shopping cart.

This training will introduce users to the new generation user interface.

Learn how to effectively use Calibre nmDRC and nmLVS in your layout verification flow and analyze the verification results.

Learn how to create a reusable testbench from ground up using SystemVerilog UVM (Universal Verification Methodology) and how to add a UVM Register Model.

Learn how to quickly build sophisticated UVM testbenches with UVM Framework, a class library, and code generator, part of the Questa® Verification Solution.

Learn how to build a UVM testbench for an IP core using UVM Framework and Questa Verification IP (QVIP).

Create a UVM Register Layer description of hardware registers and memories, integrate into a UVM testbench, and verify your design with methods and sequences.

Learn basic flows starting from configuration of the tool, input and preparation of data, and output generation (SMT programs, Stencil and documentation).

Learn to use Valor NPI to incorporate Design for Manufacturing (DFM) analysis into your PCB design process.

Learn the ODB++ data, using MRA, BOM Management, setting up and running DFM Analysis and other NPI tools to facilitate passing a PCB design to manufacturing.

Learn how to use the Visualizer Debug Environment to debug and analyze your HDL design.

Xpedition training library will offer a complete portfolio of learning paths for schematic design, constraint definition, pcb layout, and library creation and management.

Xpedition (Japanese) Training Library offers a complete portfolio of learning paths for schematic design, constraint definition, and pcb layout, in Japanese.

Learn at your own pace using this course, how to use advanced packaging functionality including cavity creation, part stacking and wire bonding.

Learn at your own pace using this course, ECAD-MCAD collaboration workflow, setup the interaction between ECAD and MCAD, map and exchange 3D models.

You will learn the basics necessary to script Xpedition Layout, Designer and Databook while watching video recordings of class presentations.

The Xpedition training library will offer a complete portfolio of learning paths using the 2409 release of the software.