On-Demand Training

This library of Tessent training courses will enable you to learn about the options for implementing high test quality in your designs.

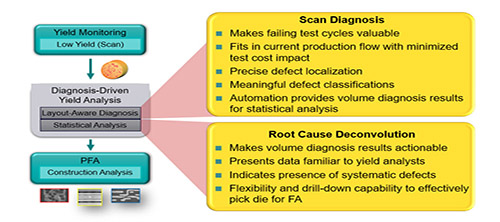

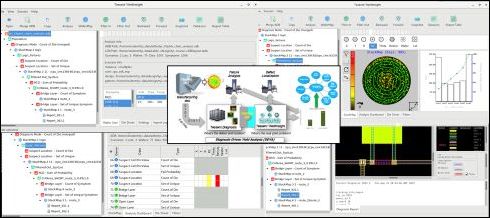

This learning path focuses on Tessent Diagnosis within the Diagnosis Driven Yield Analysis (DDYA) flow.

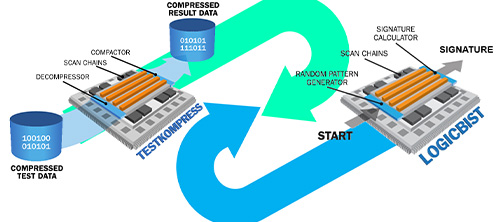

You will learn how to use Tessent TestKompress and LogicBIST together to add both types of logic to your IC to get the benefits of both solutions.

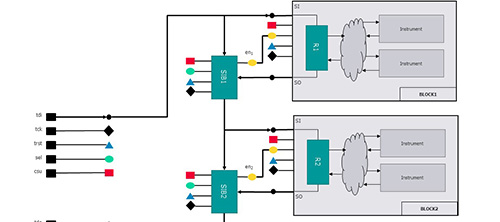

The Tessent IJTAG course covers the details of the IEEE 1687 standard, and how it is used in the Tessent toolset to enable access to the various test IPs.

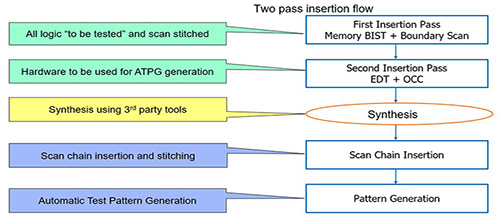

Learn how to implement MBIST, Boundary Scan, IJTAG, Scan Insertion, and TestKompress into your design to obtain high test quality using multiple Tessent tools.

You will learn how to implement DFT for memory test through Tessent Shell tool environment & how to utilize it to implement MemoryBIST solutions for your design.

In this learning path, you will learn about the structure, main concepts, and implementation of Multi-Die devices, as well as their testing and diagnosis.

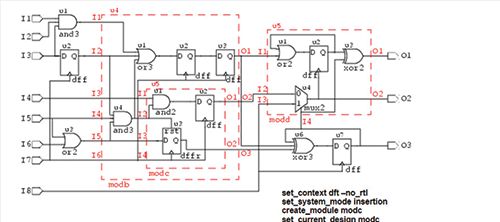

This learning path will introduce you to scan and ATPG processes. You will gain knowledge on fault models, test pattern types and at-speed testing.

You will learn how to use your Tcl knowledge to perform database introspection for reporting and for design editing for testability improvements.

You will learn how to use Tessent SiliconInsight, and understand the MBIST offline diagnosis flow, as well as ATPG offline diagnosis flow in non-TSDB.

Learn how to leverage the Tessent Shell environment to insert SSN and other test logic into SoCs, generating & verifying test patterns for manufacturing tests.

You will be introduced to Embedded Deterministic Test (EDT) technology, and you will learn how to create compressed test patterns and how to debug EDT DRCs.

This course covers the DDYA process, including is an overview of Tessent Diagnosis and how to use Tessent YieldInsight to identify the true yield limiters.